音频(WM8731芯片)输入输出试验设计Verilog代码VIVADO ARTIX

名称:音频(WM8731芯片)输入输出试验设计Verilog代码VIVADO ARTIX-7开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

音频(WM8731芯片)输入输出试验

通过耳麦说话,并通过耳机收听,音频环回功能是采用开发板音频模块电路实现M_IN口输入音频信号,同时L_OUT口输出音频信号,即L_OUT口上的扬声器能够实时的播放M_IN口输入的声音

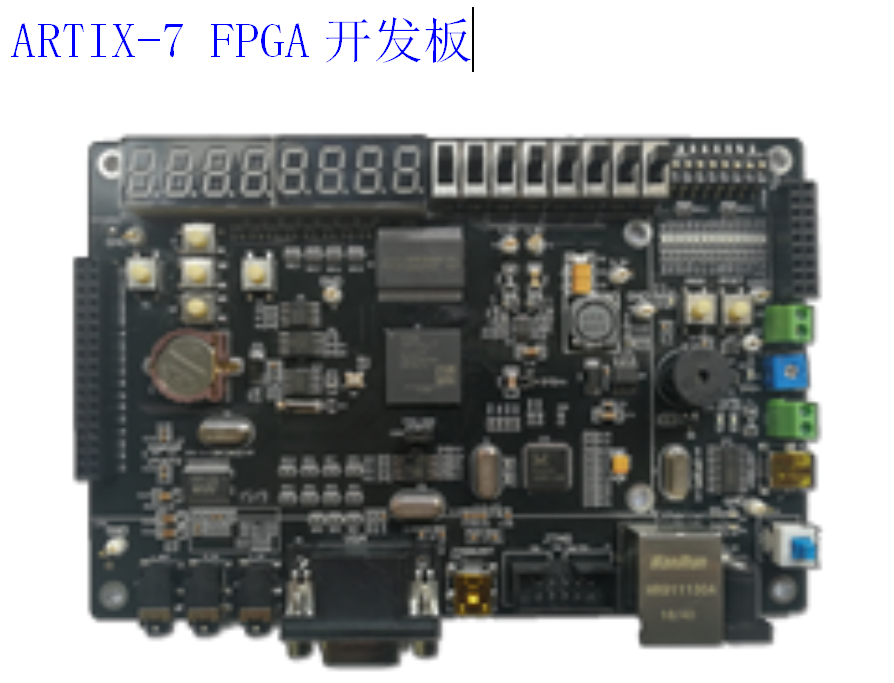

本代码已在ARTIX-7开发板验证,ARTIX-7开发板如下,其他开发板可以修改管脚适配:

1、实验简介

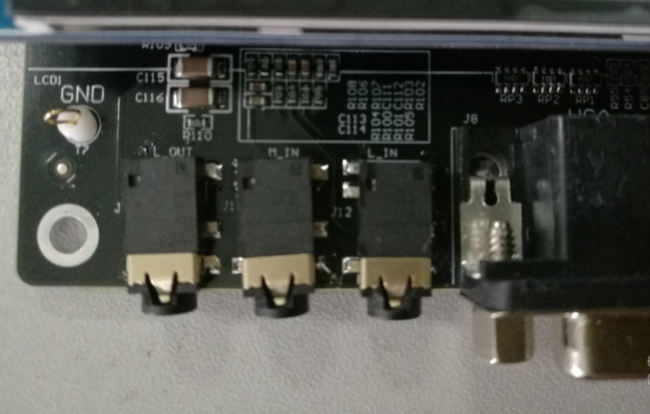

本实验的音频环回功能是采用开发板音频模块电路(如下图1.1)实现M_IN口输入音频信号,同时L_OUT口输出音频信号,即L_OUT口上的扬声器能够实时的播放M_IN口输入的声音。

图1.1 开发板音频接口

2、实验原理

2.1硬件介绍

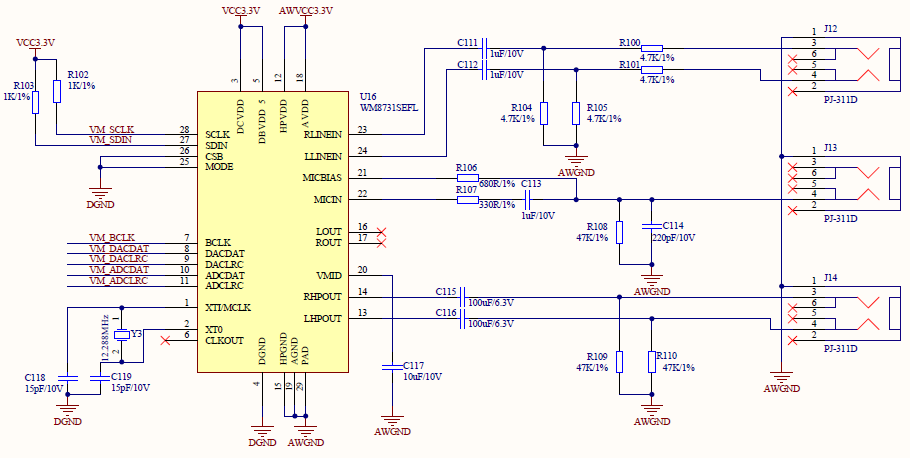

开发板音频模块使用WOLFSON公司的WM8731芯片实现声音信号的A/D和D/A转换功能。下图2.1为音频模块的硬件电路:

图2.1 音频模块电路

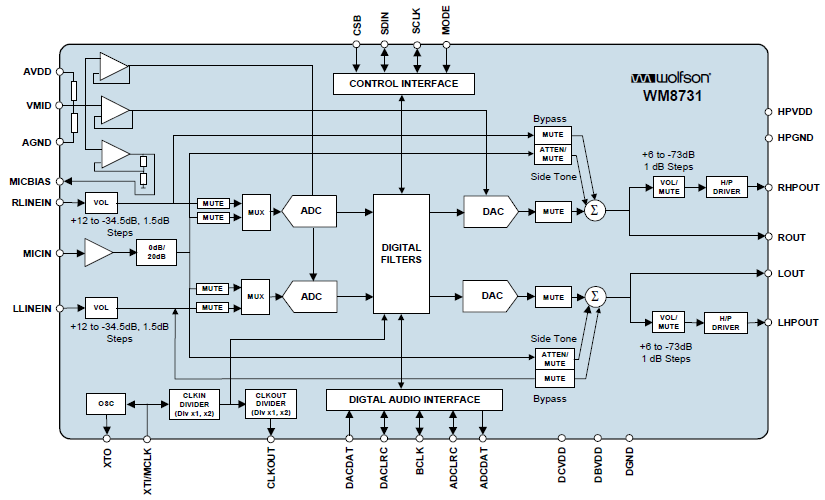

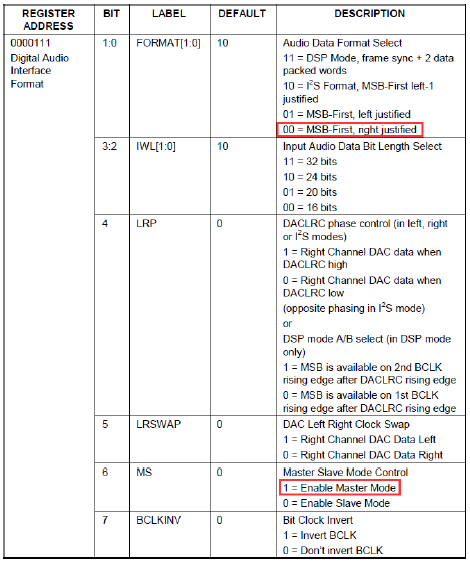

2.2 WM8731配置和时序

这里简单介绍一下音频模块用到的音频编/解码芯片WM8731。该芯片在本设计中主要完成声音信号在采集和回放过程中的A/D和D/A转换功能。该芯片的ADC和DAC的采样频率为8KHz到96KHz可调,可转换的数据长度为16-32位可调。WM8731的内部有11个寄存器。该芯片的初始化以及工作时的工作状态和功能都是通过以I2C总线方式对其内部的这11个寄存器进行相应的配置来实现的。本设计中WM8731工作于主模式,采样频率设为48KHZ, 转换的数据位长度为16位。WM8731的数字音频接口有5根引脚,分别为:BCLK(数字音频位时钟)、DACDAT(DAC数字音频数据输入)、DACLRC(DAC采样左/右声道信号)、ADCDAT(ADC数字音频信号输出)、ADCLRC(ADC采样左/右声道信号)。在本设计中FPGA为从设备,WM8731为主设备。ADCDAT、DACDAT、ADCLRC和DACLRC与位时钟BCLK同步,在每个BCLK的下降沿进行一次数据传输。BCLK、DACDAT、DACLRC、ADCLRC为WM8731的输入信号。ADCDAT为WM8731的输出信号。

图2.2 WM8731结构

在本系统中FPAG和WM8731的控制和数据通信将用到I2C和数字音频总线接口。FPGA通过I2C接口配置WM8731的寄存器,通过I2S总线接口来进行音频数据的通信。关于I2C接口,其他实验中已经有讲解,下面我们主要来了解数字音频接口。

数字音频接口可提供4种模式:

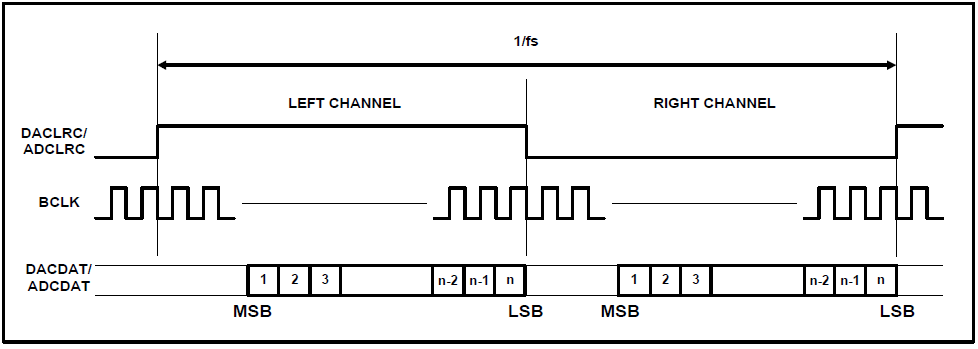

1. Right justified(如图2.3)

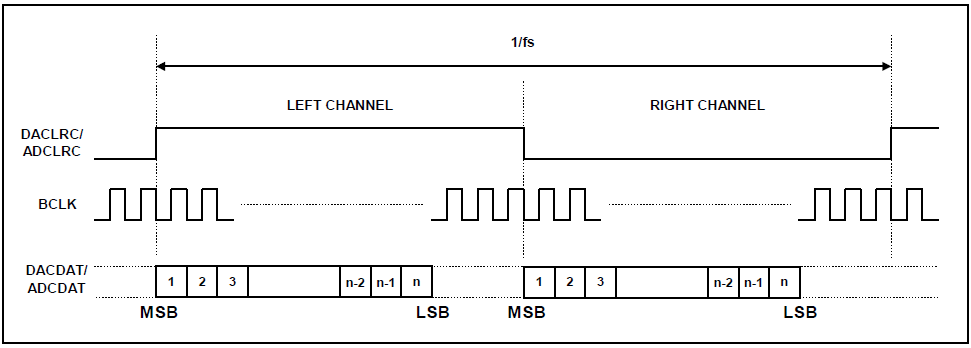

2. Left justified(如图2.4)

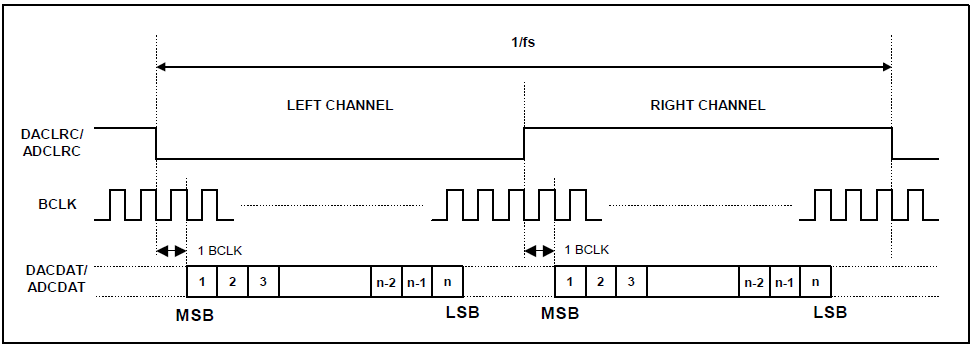

3.I2S(如图2.5)

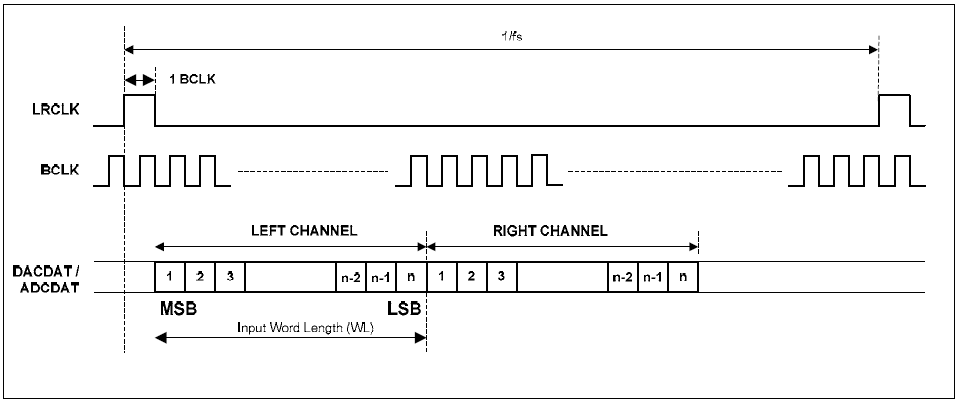

4.DSP mode(如图2.6)

图2.3 Right justified模式

图2.4 Left justified模式

图2.5 I2S模式

图2.6 DSP mode模式

本实验选择Right justified模式。

3、程序设计

本实验的功能是程序检测按键KEY是否按下,如果检测到KEY按下了,开始录音,同

时播放录取的音频。本程序包含两大部分:WM8731寄存器配置,音频接收和播放。音频环回的过程为:AD采集的音频数据直接进入DA输出。

WM8731寄存器配置

lut_wm8731 模块和i2c_config 模块将寄存器配置地址和配置信息通过查找表的形式通过I2C总线写入音频模块中,具体的请参考例程代码和wm8731 的芯片数据手册。

音频录取和播放

audio_rx 接收模块,接收从麦克风输入的语音信号,完成左右声道的音频接收,将串行数据转换成并行数据。通过“Right justified”模式的时序图可以看到接收语音信号时在LRC 信号为高电平,且BCLK 信号的上升沿时左声道接收数据并完成串行信号转换成并行信号的过程。在LRC 信号为低电平,且BCLK 信号的上升沿时右声道接收数据并完成串行信号转换成并行信号的过程。

audio_tx是音频发送模块,完成左右声道音频数据的串行化。同样通过时序图可以看到,语音信号完成模数,数模转换,在LRC信号上升沿,且即将跳变为高电平时开始发送左声道数据,BCLK信号下降沿时完成缓存将并行信号转换为串行信号的过程;在LRC信号上升沿且即将跳变为低电平时开始发送右声道数据,在BCLK信号下降沿时完成缓存将并行信号转换为串行信号的过程。

audio_key模块主要完成录音播放的按键控制,状态转换如下,当按键按下后进入录音状态,当按键松开时进入播放状态。

4、实验现象

开发板首先将音频模块插入扩展口,同时插入麦克风和耳机,然后下载实验程序,戴上耳机,用麦克风开始讲话,耳机能听到麦克风语音。

部分代码展示:

/* * Copyright (C)2014-2015 AQUAXIS TECHNOLOGY. * Don't remove this header. * When you use this source, there is a need to inherit this header. * * License * For no commercial - * License: The Open Software License 3.0 * License URI: http://www.opensource.org/licenses/OSL-3.0 * * For commmercial - * License: AQUAXIS License 1.0 * License URI: http://www.aquaxis.com/licenses * * For further information please contact. *URI: http://www.aquaxis.com/ *E-Mail: info(at)aquaxis.com */ //// Company: ALINX黑金// Engineer: 老梅// // Create Date: 2016/11/17 10:27:06// Design Name: // Module Name: mem_test// Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //module aq_axi_master( // Reset, Clock input ARESETN, input ACLK, // Master Write Address output [0:0] M_AXI_AWID, output [31:0] M_AXI_AWADDR, output [7:0] M_AXI_AWLEN, // Burst Length: 0-255 output [2:0] M_AXI_AWSIZE, // Burst Size: Fixed 2'b011 output [1:0] M_AXI_AWBURST, // Burst Type: Fixed 2'b01(Incremental Burst) output M_AXI_AWLOCK, // Lock: Fixed 2'b00 output [3:0] M_AXI_AWCACHE, // Cache: Fiex 2'b0011 output [2:0] M_AXI_AWPROT, // Protect: Fixed 2'b000 output [3:0] M_AXI_AWQOS, // QoS: Fixed 2'b0000 output [0:0] M_AXI_AWUSER, // User: Fixed 32'd0 output M_AXI_AWVALID, input M_AXI_AWREADY, // Master Write Data output [63:0] M_AXI_WDATA, output [7:0] M_AXI_WSTRB, output M_AXI_WLAST, output [0:0] M_AXI_WUSER, output M_AXI_WVALID, input M_AXI_WREADY, // Master Write Response input [0:0] M_AXI_BID, input [1:0] M_AXI_BRESP, input [0:0] M_AXI_BUSER, input M_AXI_BVALID, output M_AXI_BREADY, // Master Read Address output [0:0] M_AXI_ARID, output [31:0] M_AXI_ARADDR, output [7:0] M_AXI_ARLEN, output [2:0] M_AXI_ARSIZE, output [1:0] M_AXI_ARBURST, output [1:0] M_AXI_ARLOCK, output [3:0] M_AXI_ARCACHE, output [2:0] M_AXI_ARPROT, output [3:0] M_AXI_ARQOS, output [0:0] M_AXI_ARUSER, output M_AXI_ARVALID, input M_AXI_ARREADY, // Master Read Data input [0:0] M_AXI_RID, input [63:0] M_AXI_RDATA, input [1:0] M_AXI_RRESP, input M_AXI_RLAST, input [0:0] M_AXI_RUSER, input M_AXI_RVALID, output M_AXI_RREADY, // Local Bus input MASTER_RST, input WR_START, input [31:0] WR_ADRS, input [31:0] WR_LEN, output WR_READY, output WR_FIFO_RE, input WR_FIFO_EMPTY, input WR_FIFO_AEMPTY, input [63:0] WR_FIFO_DATA, output WR_DONE, input RD_START, input [31:0] RD_ADRS, input [31:0] RD_LEN, output RD_READY, output RD_FIFO_WE, input RD_FIFO_FULL, input RD_FIFO_AFULL, output [63:0] RD_FIFO_DATA, output RD_DONE, output [31:0] DEBUG); localparam S_WR_IDLE = 3'd0; localparam S_WA_WAIT = 3'd1; localparam S_WA_START = 3'd2; localparam S_WD_WAIT = 3'd3; localparam S_WD_PROC = 3'd4; localparam S_WR_WAIT = 3'd5; localparam S_WR_DONE = 3'd6; reg [2:0] wr_state; reg [31:0] reg_wr_adrs; reg [31:0]

源代码

点击下方的公众号卡片获取

分享让更多人看到

热门排行

- 1云计算:OpenStack 云主机实例资源配置实现内网互通

- 2Spring AI 使用本地 Ollama Embeddings

- 3安卓 vs iOS 深入分析文件系统:开放自由和封闭安全的终极游戏

- 4Java【代码 17】httpclient PoolingHttpClientConnectionManager 例子用于连接池

- 5如何在SQL中高效使用聚合函数、日期函数和字符串函数:实用技巧与案例解析

- 6Datawhale X 魔搭 AI夏令营

- 7【LeetCode力扣】42. 接雨水

- 8Java【代码 17】httpclient PoolingHttpClientConnectionManager 例子用于连接池

- 9云计算:OpenStack 云主机实例资源配置实现内网互通

- 10外国媒体称英伟达RTX 50系显卡发布表现不佳 有很多问题